指令流水线

前言

第6章(指令流水线)主要介绍指令流水线的基本原理、流水段寄存器的概念、流水线数据通路的设计、流水线的控制信号、结构冒险及其处理、数据冒险及其处理、转发技术、控制冒险及其处理、分支预测原理、超标量和动态流水线的概念和技术。

流水线数据通路和控制逻辑

流水线的执行效率

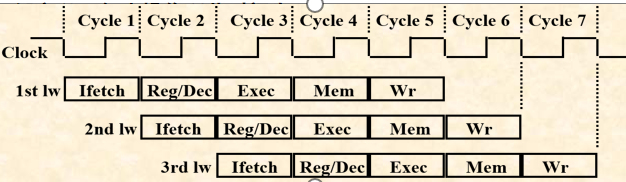

- 流水线的组成:

- 取指令IF(ifetch)—到内存取指令并计算PC+4,运用到加法器、内存、PC

- 译码ID—取数同时译码

- 取操作数OF—取数同时译码,运用到寄存器堆读口、译码器

- 执行EX—计算地址,运用到加法器、扩展器(16位扩充至32位)、ALU

- 写回WB—将数据写到寄存器,运用到寄存器堆写口

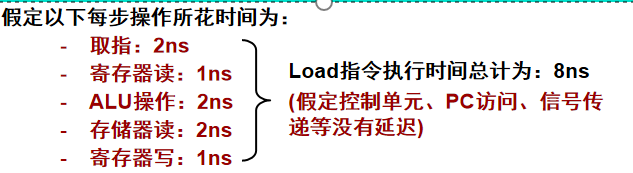

单周期指令

- 时钟周期=所有步骤所花时间—2+1+2+2+1=8ns

- 串行执行时,N条指令的执行时间:8Nns

- 每条指令只在一个周期内完成

流水线性能

- 时钟周期=最长的指令执行时间:2ns

- 流水线方式执行时,N条指令的时间:2(N-1)+10=(4+N)*2ns≈2Nns,所以N很大时,比串行方式快4倍

- 每条指令的执行时间:2ns*5=10ns,因此流水线不能缩短每一条指令的执行时间

流水线指令集的设计

- 指令长度一致—利于取指、译码

- 如MIPS指令32位,取下一条指令为PC+4

- 格式规整,保证源寄存器的位置相同—利于指令未知时候取寄存器操作数。

- 如,寄存器Rs和Rt的位置一定

- 采用装入/存储型(load/store)指令风格—利于减少操作步骤

- 内存中“对齐”存放—利于减少访存次数和流水线的规整

- 地址是信息的整数倍,如MIPS指令为4字节32位,存放按4的倍数,即低2位是00,例如4(0100)和8(1000)

MIPS指令的流水段分析

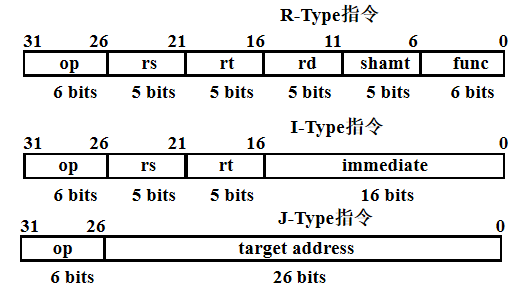

- R-Type

- 在ALU中对rs和rt内容运算,把运算结果送目的寄存器rd。遇到add和sub指令还要判断是否溢出,不溢出才写到rd

- I-Type

- 立即数的运算类指令要对16位立即数进行符号扩展/零扩展,和rs内容运算,送到rt寄存器。

- J-Type

- 无条件转移指令,直接将目标地址送PC中。

OP:操作码

rs:第一个源操作数寄存器

rt:第二个源操作数寄存器

rd:结果寄存器

shamt:移位指令的位移量

func:R-Type指令的OP字段是特定的“000000”,具体操作由func字段给定。例如:func=“100000”时,表示“加法”运算。

immediate:立即数或load/store指令和分支指令的偏移地址

target address:无条件转移地址的低26位。将PC高4位拼上26位直接地址,最后添2个“0”就是32位目标地址。

流水线冒险处理

高级流水线技术

All articles in this blog are licensed under CC BY-NC-SA 4.0 unless stating additionally.

Comment